【ZiDongHua 之品牌自定位收录关键词:新思科技 SoC 机器学习 】

如何加快数十亿门级低功耗SoC验证?

数字社会,似乎人人都离不开智能手机。如今的智能手机不仅功能五花八门、支持多任务处理,还有较长的续航时间,这表明移动设备开发者在电源管理方面谨慎地做了权衡。如今手机中的芯片通常具有数十亿个门,超过2000万行代码以及数百个电源域。要让这样的设备在能效表现上保持最佳水平,需要找到合适的平衡点。

多年来,芯片开发者一直在优化SoC,设法让芯片的某些部分在闲置时进入睡眠模式。比如,在智能手机上使用地图App时,手机芯片中负责运行电子邮件系统的部分便可以关闭。但是,确保芯片时刻为使用做好准备则是一项艰巨的任务。

鉴于如今低功耗SoC的规模和复杂性,验证和签核工作只会变得愈发具有挑战性。然而,这些环节却比以往任何时候都更加重要,因为有些错误如果未被发现,可能对芯片有害,甚至带来更严重的影响。不过,SoC验证技术已经有了很大的发展,能够支持如今大规模的芯片设计。例如,新思科技的VC LP?静态低功耗验证解决方案提供了650多项检查功能,并具备全芯片验证功能和性能,能够实现完整的低功耗静态签核。目前,该解决方案还增加了高级功能检查,有助于验证开发者找到潜在的功能问题。如果等到仿真过程中再来检测这些问题,则会非常耗费资源。本文将展开探讨新思科技的VC LP解决方案如何助力实现更快、更全面的调试,帮助开发者打造高质量、高性能芯片。

通过机器学习和层次化方法加快SoC调试

从智能手机到服务器和各种网络设备,如今越来越多的电子产品都离不开高级电源管理功能。借助各种低功耗SoC设计技术,比如功率门控、保留单元、低VDD待机、隔离单元的使用和动态电压率调整(DVS),开发者可以使用行业标准IEEE 1801统一电源格式(UPF)功耗设计意图语言作为通用语言来指定设计的功耗设计意图,实现精细化电源管理。但是,这些技术也会在设计流程的不同阶段增加新的设计元素。鉴于低功耗SoC的设计架构和行为性质,其芯片验证和签核要比永不断电的SoC设计更具挑战性。

VC LP静态检查解决方案有助于增强和加快调试过程,确保仿真过程专注于捕获动态低功耗错误。新思科技VC LP解决方案可在RTL上或综合及布局布线后运行,能够比传统方法更早、更快地捕获低功耗错误。该解决方案还具备在整个设计流程中全面运行低功耗静态检查的重要能力,能够准确验证设计的正确实现和行为。

虽然这种静态检查工具通常是在小模块(比如IP级别)上运行的,但该VC LP解决方案已扩展为能够在更大的模块、更大的设计,甚至是整个芯片上运行。在该解决方案中,多线程解决了运行时问题,而机器学习(ML)驱动的引擎则能为开发者指出问题所在及其根本原因和影响。下面我们介绍其中两项最新的功能。

图片

机器学习驱动的根本原因分析

如今的一些大型设计可能存在多达一百万个违例,因此如果解决方案能够智能地对问题进行分类并提供解决问题的线索,便可帮助开发者节省大量的时间和精力,让其专注于分析违例原因并解决问题。事实上,通过手动调试来管理签核过程中报告的大量问题并不可行,而且容易出错。

图1:新思科技VC LP中机器学习驱动的根本原因分析结果

新思科技VC LP解决方案具有机器学习驱动的根本原因分析功能,能够创建“智能分组”并向开发者提示准确的根本原因,帮助减少调试时间。开发者可以将现有违例分类到智能集群中,以此捕获违例原因和违例影响,从而专注于分析违例原因并修复问题。

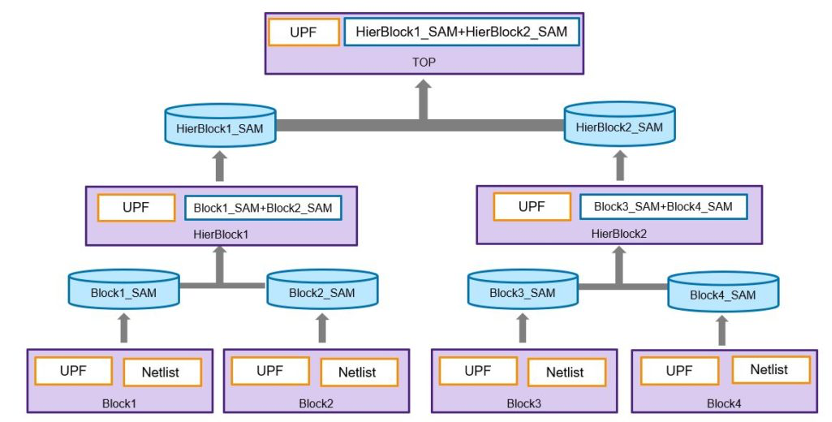

静态抽象模型

新思科技VC LP解决方案中的静态抽象模型(SAM)能够以最佳结果质量(QoR)实现层次化验证,与展平运行相比,性能更出色。这些模型仅包含与顶层或其他模块交互的块级逻辑部分,完全包含在块内的所有连接或路径都将被舍弃。顶层集成者以专注于顶层违例和集成,而不必担心层次结构深处通常由块所有者解决的违例。通过SAM流程,客户可实现高达15倍的容量和运行时间增益,同时减少内存使用量。

图2:新思科技VC LP静态抽象模型层次结构

总结

从智能手机到服务器,各种功耗敏感型设备和系统需要低功耗SoC,以提供预期性能和所需能效。虽然先进的电源管理技术有助于实现预期结果,但也加大了低功耗设计的验证和签核难度。凭借最新的增强功能,新思科技的VC LP静态低功耗验证解决方案可以帮助开发者在开发早期发现与功耗相关的错误并予以修复。鉴于当今低功耗SoC的规模和复杂性,如果调试辅助工具具备机器学习能力和大规模容量,足以帮助开发者更轻松地打造出色的产品。

评论排行