加特兰先进封装迈向“Next Level”,持续引领智驾雷达芯高度

随着汽车智能化的发展,提升智能感知芯片的性能、满足车载雷达应用差异化的需求已成为推动行业进步的关键驱动力。作为毫米波雷达芯片领军企业,加特兰不仅在芯片层面持续革新,也早在2017年开始投入先进芯片封装技术的研发。除标准封装雷达芯片以外,加特兰先后推出了具有创新性的封装集成片上天线(Antenna in Package,AiP)雷达芯片与ROP®(Radiator on Package)雷达芯片。在汽车毫米波雷达芯片领域,加特兰的先进封装技术已“Next Level”,引领行业新高度。

左右滑动查看更多照片

11月22日,先进封装开发者大会在沪举办,加特兰生产技术总监王典博士受邀发表主题演讲,与业界分享了加特兰先进封装技术在车载毫米波雷达芯片中的应用及设计。王典博士介绍道:“加特兰先进的封装技术与传统封装技术不同,我们把封装做成了‘功能组件’,也就是把某些雷达功能实现,集成到了封装中。比如,AiP技术集成了天线,ROP®技术集成了配合波导天线的辐射体。”目前,加特兰已布局芯片封装技术相关专利72件,其中标准封装技术9件、AiP技术相关39件、ROP®技术相关24件。

标准封装

加特兰芯片的标准封装技术,以eWLB(Embedded Wafer-Level Ball Grid Array,嵌入式晶圆级球栅阵列封装)为主,采用尽可能短的信号路径连接芯片与封装,最大程度降低射频链路损耗,广泛应用于加特兰各个系列的毫米波雷达SoC芯片中,为传统毫米波雷达模组带来低成本和高技术成熟度的优势。

AiP封装

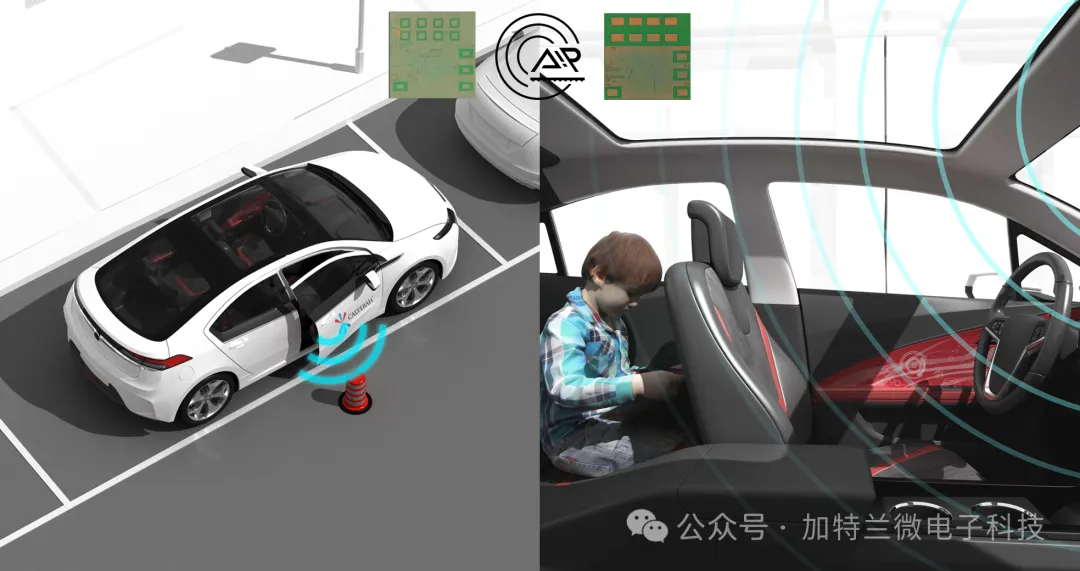

加特兰是全球首屈一指的规模量产AiP SoC的毫米波雷达芯片企业。加特兰的AiP技术主要基于FCCSP(Flip Chip Chip Scale Package,倒装芯片级封装)设计。相较标准封装芯片,采用AiP技术的SoC芯片,可以进一步提升雷达模组的集成度,减小模组尺寸,并降低模组成本。从最早基于Alps平台的Alps AiP SoC、Rhine AiP SoC、Rhine-Mini AiP SoC,到最新一代Kunlun平台的Kunlun-USRR AiP SoC与Lancang-USRR AiP SoC,加特兰持续迭代优化AiP封装技术。目前,加特兰AiP雷达芯片产品已广泛应用于门雷达、APA(Automatic Parking Assist,自动泊车辅助)雷达、舱内雷达等对汽车安装环境要求严苛的应用场景,实现自动门开门避障、车身周围环境探测、儿童存在检测(CPD)等功能。在AiP天线设计方面,加特兰提供很高的设计冗余度,确保芯片能够实现稳定大规模量产,同时能保证芯片在不同场景下的可靠性。

ROP®封装

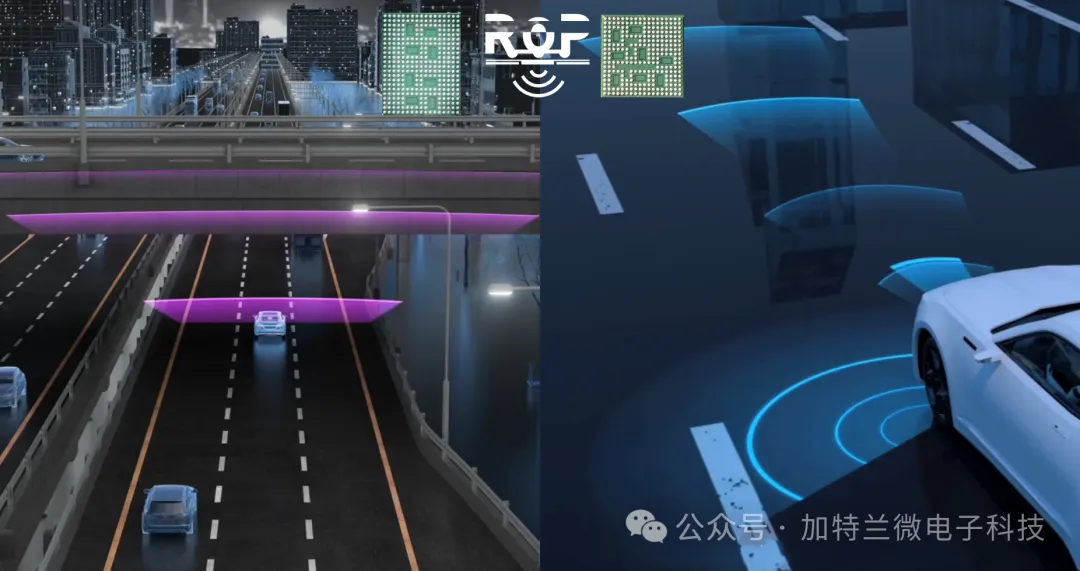

ROP®技术代表了加特兰最前沿、最革新的毫米波封装技术。同样基于FCCSP,该技术通过辐射体(Radiator)将信号直接传输到波导天线系统,大幅减少天线馈线损耗的同时,显著提高通道隔离度,性能得到极致提升。目前,加特兰ROP®封装应用于Alps-Pro和Andes系列SoC芯片,配合波导天线系统,显著提升雷达的探测性能和角度分辨能力,助力高性能智驾雷达的实现。

“过去的封装,设计目的是实现信号互连;而我们要将雷达功能实现在封装上,需要考虑的方面与传统封装设计不同,也就是更全面的协同仿真。”王典博士在分享中说道。加特兰充分利用先进的仿真工具,与封装供应商紧密合作,对封装结构、材料以及热、电、磁、力等多物理场效应进行精确模拟,以预测并优化封装在各种环境下的性能表现。这一过程不仅涵盖了封装内部的互连结构、散热设计等关键要素,还深入考虑了封装与外部环境的相互作用,对芯片进行深入模拟和分析,保证、提升了封装可靠性的同时,更充分考量了雷达性能的实现和优化。

创新,作为加特兰的核心价值观之一,写在了加特兰的企业基因里。我们希望持续保持技术前瞻性,不断探索和突破,深入车规无线半导体研发,提升芯片封装技术的水平与质量,为客户提供更丰富多样的芯片产品选择,助力智能驾驶、智能座舱,以及工业消费领域的创新发展。

评论排行