高峰对话 | 国微芯携先进制程工艺解决方案亮相ICDIA

7月13-14日,国微芯应邀参加中国集成电路设计创新大会暨IC应用博览会(2023无锡)产品展与高峰论坛,为大家展示先进制程工艺解决方案。国微芯执行总裁兼首席技术官白耿先生在论坛上发表题为《半导体工艺超线性发展对国产EDA的机遇和挑战》的精彩演讲,分析了先进制程工艺带来的挑战,并介绍了国微芯的突破路径。

根据ITRS 2.0(国际半导体技术路线图)报告,先进逻辑制程主要由FinFET、FD-SOI、GAA工艺引导,这是三种不同的晶体管工艺。由于通道厚度的缩放限制,FD-SOI工艺在11/10nm节点处结束,而FinFET工艺受鳍片宽度的缩放限制,在6/5nm节点处结束(实际最小至3nm)。未来5-10年,先进芯片制造将追求比3nm更小的节点,GAA (Gate All Around)工艺被IMEC正式推荐为未来五年的首选工艺,以此突破FinFET的器件性能限制。

多个先进制程工艺给芯片制造带来了诸多难关。举例来说,多鳍FinFET需要非常复杂的图案化步骤和多个掩膜,GAA的全流程图案化对EUV OPC的复杂度和软硬件性能提出了巨大挑战。此外,图形化方法也是一个难以克服的问题。例如,金属层对光刻的工艺窗口要求极其严格,双重或多重图案化(SADP/SAMP)需要多个掩膜,导致复杂度和成本极高,2Dpatterning也具有困难性……

为了突破先进制程工艺和图形化方法带来的多重挑战,国微芯开发了核心后端和制造端EDA工具,为国内先进制程和IC设计提供了定制化技术支持。

国微芯带你

直击峰会现场

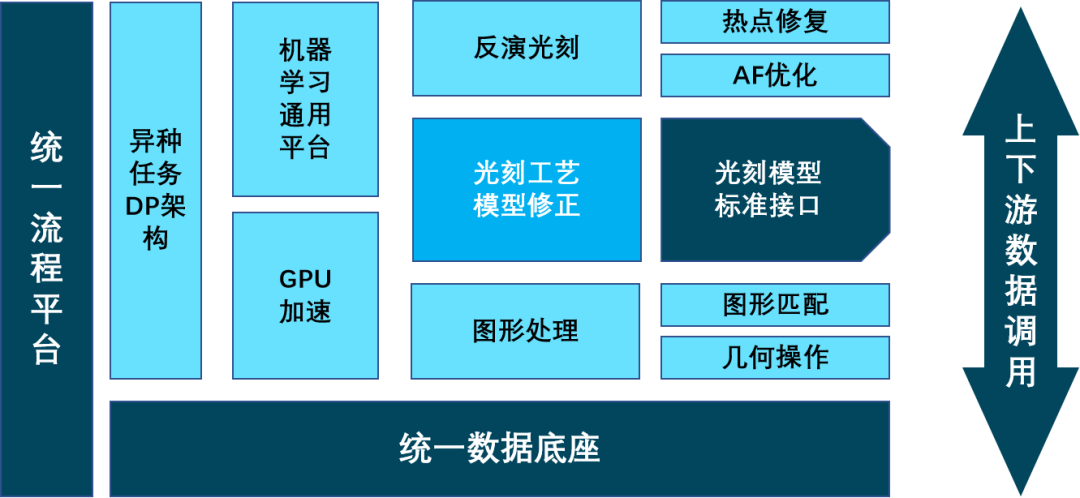

此次会议交流,国微芯详细展示了出色成果——光刻掩模优化平台EsseOPC。该平台完全自主可控,兼顾国产替代及未来先进工艺的应用,在前沿的光刻模型、反刻光演和数据库海量高速读写及交换技术等方面有丰厚的技术积累和Ips。

EsseOPC支持以DUV光刻过程实现的14nm及更先进工艺节点生产的核心技术,并已和多家国内Foundry厂达成合作。此外,计划于不久后,EsseOPC达到支持极限分辨率之下的掩膜合成工艺、浸润式ArF DUV制程、Logic DRAM×NAND工艺、OPC×ILT×RET全流程以及掩膜厂工艺。

白耿先生指出,在IC制造领域,业界需要充分的技术储备以适应不断变化的形势,并逐步实施不受尖端设备影响的特殊工艺突破,如背面供电SOI技术、3D封装新方案等。在有条件的情况下,最好及时跟进实用化的新工艺。

展位现场,国微芯高度完备的EDA工具链吸引了观众的关注,纷纷驻足了解。这些EDA工具以传统哲学"大道至简,悟在天成"为灵感,被命名为"芯天成",英文名为”Esse”(本质)。

芯天成各系列不仅功能强大、性能卓越,而且还拥有用户友好的界面和操作方式,能够提高设计师的工作效率和设计质量,降低学习成本。

观众们对国微芯的技术实力和创新能力表示高度认可和赞赏,许多参会者与国微芯的技术人员进行了交流和咨询。本次博览会上国微芯收获了广泛关注,充分展示了EDA在集成电路产业发展中的重要性。

未来,国微芯将继续探索并践行集成电路产业发展规律,以强大的研发力量为基础,以全流程EDA工具链为支撑,以“自主创新、让造芯更便捷”的愿景为不断前行的动力,助力IC设计与制造,为集成电路产业发展贡献力量。

评论排行