【ZiDongHua 之电子设计自动化收录关键词: Cadence 版图自动化 电子设计自动化】

CadenceLIVE China 2023丨模拟定制设计专题议程揭晓

作为目前中国 EDA 行业覆盖技术领域全面、规模巨大的先进技术交流平台,CadenceLIVE China 2023 中国用户大会将于 8 月 29 日在上海浦东嘉里大酒店盛大举行,现场参会注册现已开放,诚邀您前来参会。

CadenceLIVE 在中国已成功举办近 20 届,时隔三年再次从线上走到线下,CadenceLIVE China 2023 中国用户大会有众多亮点值得关注,您绝对不容错过!

今天我们向您介绍此次会议专题之一:

模拟定制设计专题

在此次模拟定制设计专题中,Cadence 将会介绍最新一代 Virtuoso Studio 和 Spectre 平台的新的技术演进和功能,覆盖整个定制设计的完整流程。并且我们邀请了 Cadence 在中国的合作伙伴分享在实际工作中,他们如何应用 Cadence 的定制设计和仿真验证工具,提高设计验证效率及交付质量以应对越来越高的设计挑战及紧迫的交付周期。

分享的内容涵盖:

Spectre 后仿加速方法学

Spectre FX 和 AMS-Spectre FX在大规模电路仿真上的应用

版图自动化

EMIR 分析

SRAM 电路特征化提取

PDK 开发等方面

部分议题抢先看

基于 Virtuoso Device-level APR 流程实现版图设计的效率提升

Finfet 工艺的复杂性对版图设计者带来更大的挑战,本文阐述使用 Virtuoso Device-level APR 流程进行 Finfet 工艺定制版图自动化的设计,快速得到一个满足 coloring 及 DRC 规则的定制版图。

Several Techniques About Post-Layout Simulation in RF/Analog Design

此议题将详细阐述多种在 Virtuoso 环境中用 DSPF 进行后仿的方法及如何灵活应用 Cadence 工具避免后仿中的问题,提供的 dspf 后仿真方法实用,尤其是 dspf 多 corner 仿真。

一种基于 Quantus-Reduce 加速模拟仿真验证分析的解决方案

此议题将介绍 Quantus 寄生抽取工具的 qreduce 功能,集合实例讲解网表精简原理,解决了庞大寄生网表造成仿真速度慢的问题,大大加快芯片设计的迭代速度.对所有后仿真设计均有借鉴意义。

使用新一代 Fast Spice 仿真器 – SpectreFX 实现 SerDes 电路全面高效验证

现代 SerDes 电路规模越来越大,工作频率也越来越高,电路全面仿真验证耗费的时间越来越长,在这个议题中,我们将集合实例介绍了如何使用新一代 Fast Spice 仿真器 Spectre FX 来加速 SerDes 电路验证。

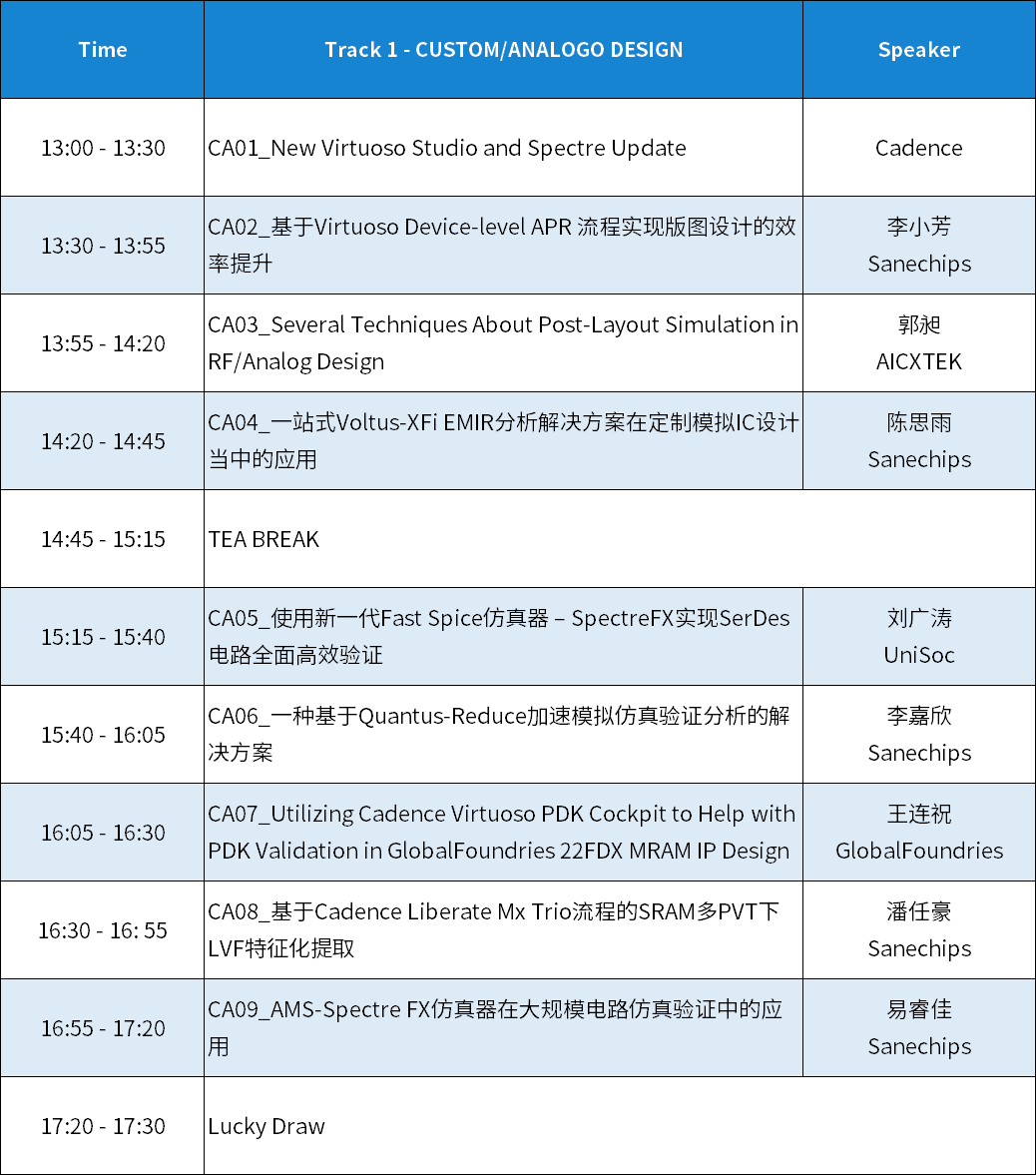

专题议程

*日程以最终现场公布为准

8 月 29 日活动当天,设有八大分会场,聚焦验证、PCB 封装设计及系统级仿真、模拟定制设计、数字设计和签核、汽车电子和 IP 解决方案、AI 和大数据分析等 6 大专题,涉及人工智能(AI)、大数据、汽车电子、网络通信、5G/6G、新能源、工业自动化等众多应用方向,以及 60+ 技术主题分享。我们之后将逐一为您揭晓!

专题议程

●

CadenceLIVE China 2023丨AI 和大数据分析专题议程揭晓

●

CadenceLIVE China 2023丨验证专题 1 议程揭晓

●

CadenceLIVE China 2023丨验证专题 2 议程揭晓

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。

评论排行