北大EDA | HeteroPlace v0.2 版本发布:重大特性升级!

【ZiDongHua 之设计自动化收录关键词:HeteroPlace EDA 电子设计自动化】

北大EDA | HeteroPlace v0.2 版本发布:重大特性升级!

快速布局布线工具助力缩短设计周期,

提升设计质量

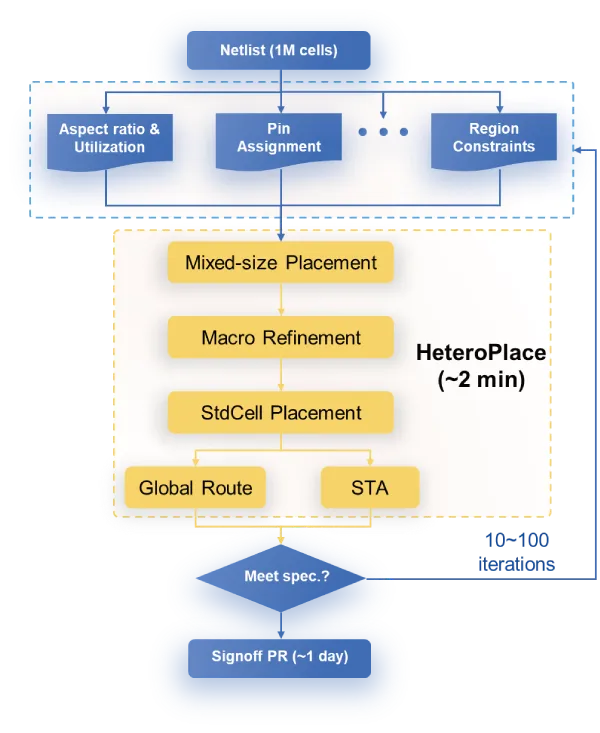

物理设计在数字集成电路的后端设计中扮演着至关重要的角色。它将逻辑综合后的设计,即标准单元和互连的图表示,转化为由逻辑门的物理形状组成的几何表示。

在整个物理设计流程中,布局具有关键的地位。作为设计流程中承上启下的步骤,布局不仅为电路综合提供了重要的指导信息,还决定了整个物理设计在核心PPA(功耗、性能、面积)指标上的表现。

HeteroPlace是无锡北京大学电子设计自动化研究院推出基于异构计算加速的快速布局工具。

HeteroPlace基于先进的异构计算架构,支持异构计算的全局布局(global placement)算法,详细布局(detailed placement)算法,全局布线(global routing)算法和静态时序分析(static timing analysis)算法,支持时序驱动(timing-driven)以及可布线性驱动(routability-driven)的布局优化算法以获得高质量的布局结果。对比基于多核CPU的传统布局算法,HeteroPlace实现了数倍到数十倍的运行时间加速,可以辅助设计者在芯片研发周期内尝试更多的实现方案,探索更有竞争力的芯片设计。

HeteroPlace作为一个快速布局工具,既可以帮助后端设计人员快速评估多种实现方案的质量,为最终signoff布局布线流程提供更好的物理规划(如模块物理形状、宏模块位置、区域划分等等),也可以帮助前端设计人员快速评估每种模块架构在最终物理实现的PPA,实现物理感知的前后端融合设计流程,以跨层次的优化方法完成更有竞争力的设计。

HeteroPlace v0.2 版本发布:

重大特性升级

我们很高兴地宣布,自2023年11月发布第一个版本后,Heteroplace v0.2 版本已完成,带来了诸多重要特性升级:

01

新增基于Python的API,支持用户在python shell中调用数据库和布局布线功能,无缝对接常用的AI框架。支持用户自主开发基于AI的EDA工具或设计流程。

02

支持所有的region constraints,包含default region, fence region和guide region。大幅降低所需要的显存占用,16G显存的消费级显卡即可满足千万单元的模块布局。

03

新增自研的基于GPU的全局布线器,数秒内完成百万门级单元设计的布线并评估congestion,支持用户自定义布线资源预占,预留power plan和CTS所需要的布线资源。

04

自研的基于GPU的时序分析工具新增对大部分时序约束的支持,包含false path,multi-cycle path,multi-clock domain等。

05

优化数据底座,支持大部分常用的LEF DEF语法。

06

修复诸多bug,进一步提升了软件的稳定性。

我要收藏

0个赞

评论排行