鸿芯微纳王宇成:谈EDA点工具的深度融合| IDAS设计自动化产业峰会演讲预告

鸿芯微纳王宇成:谈EDA点工具的深度融合| IDAS设计自动化产业峰会演讲预告

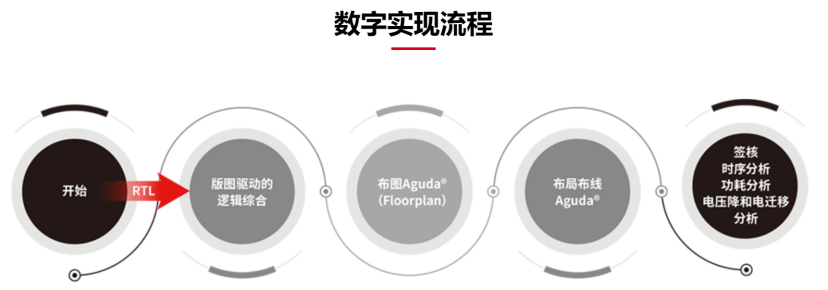

数字电路设计各个流程当中,以门级网表的产生为界,分为数字前端和数字后端。数字后端设计流程负责将前端设计生成的门级网表实现为可生产的物理版图,通过自动布线在版图上为单元、宏模块等进行合理布线;然后进行验收,对设计数据进行复检,保障数据达到交付标准,消除设计上的功能和物理缺陷,形成可以交付晶圆代工厂流片的晶圆和版图。

国外供应商经过几十年的整合,已有多家公司能够提供集成和完整工具链,而国内工具的覆盖率还不到7成,因而企业们往往将自己的目标锁定在“全流程”与“全产业链”上。国内就有一家企业聚焦数字后端,形成强大的工具链,实现国产数字芯片后端全流程,它就是深圳鸿芯微纳技术有限公司。

深圳鸿芯微纳技术有限公司成立于2018年,是一家致力于国产数字芯片电子设计自动化(EDA)研发、生产和销售的高科技公司。旨在通过自主研发、技术引进、合作开发等模式,完成数字EDA关键节点的技术部署,打造完整的国产数字芯片全流程工具链,实现产业链的技术突破;企业依托国内完整的产业生态,组建专业的研发和支持团队,建设具有竞争力的技术平台,致力于在广阔的应用领域,为全球芯片设计业提供全方位的解决方案和技术服务。

鸿芯微纳现有四大主要产品:以布线为中心的布局布线工具 Aguda?、版图驱动的逻辑综合工具 RocSyn?、静态时序签核工具 ChimeTime?以及功耗签核工具 HesVesPower?。

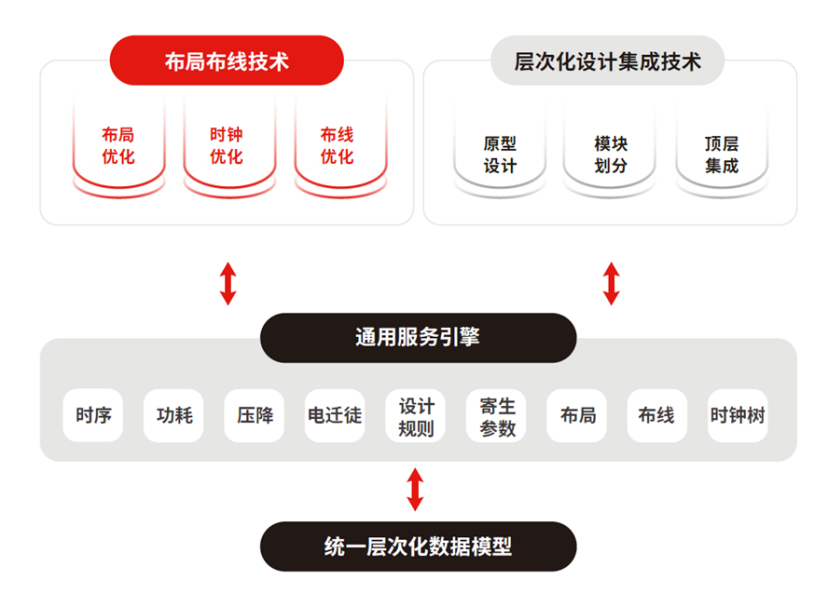

以布线为中心的布局布线工具 Aguda?

与传统工具相比,Aguda?的时序收敛速度提高了2倍以上,其超高的设计质量大幅提高了超大规模数字集成电路设计效率。解决方案已在业界头部客户得到验证,并多次成功投片。

版图驱动的逻辑综合工具 RocSyn?

逻辑综合是芯片设计中的关键步骤,RocSyn?实现逻辑综合的完整流程:经过编译、高层次优化、逻辑优化、工艺映射、时序优化等步骤将用户设计中的硬件描述语言转换成门级网表,达到一流的性能指标(延时,面积,功耗,即PPA)。

静态时序签核工具 ChimeTime?

ChimeTime?是一种静态时序签核工具,提供了SPICE仿真精度的签核结果。其搭载了独特的分布式处理能力,可在数百颗CPU上并行运行,快速完成大规模设计的分析。支持先进的CCS模型,具有针对低功耗设计先进的延迟、串扰计算引擎。支持各种OCV(包括LVF)格式。支持快速PBA时序分析能力。

功耗签核工具 HesVesPower?

功耗签核工具HesVesPower?,对全芯片系统进行功耗,电源,和信号完整性分析以及相关模型抽取。是数字后端实现和系统集成之间的关键签核步骤。

在9月18日于武汉举办的首届IDAS设计自动化产业峰会中,鸿芯微纳也将携全线产品精彩亮相。同时,鸿芯微纳首席技术官、联合创始人王宇成博士将于9月18日上午的主论坛,带来主题为“为获取更高芯片性能——谈EDA点工具的深度融合”的演讲。他将与我们分享关键点工具的开发、完善自研或合作工具链以及寻求产品差异化等话题,为我们讲述鸿芯微纳如何一步一步“把点工具做强,再把点工具串成链”。

IDAS设计自动化产业峰会预计邀请国内外300+半导体上下游企业、600+技术大咖、50+院士及专家学者、50+重磅嘉宾进行主题演讲,涵盖了从器件和电路级到系统级、从模拟到数字设计以及制造等EDA相关话题。峰会还将邀请国家发展和改革委员会、工业和信息化部、国家标准化管理委员会、国家互联网信息办公室等,部分领导已确认参会、致辞。群贤毕至,旨在(相关部委领导)对当前半导体产业发展宏观态势及未来趋势作出高屋建瓴的剖析,把脉行业发展方向。

本次IDAS设计自动化产业峰会由一场主论坛和多场平行主题分论坛组成。其中,分论坛主题初拟为:数字逻辑设计与验证领域,物理实现领域,泛模拟与封装领域,工艺模型领域,晶圆制造领域、存储器设计与制造企业专场等方向。同时,峰会现场还设置了30+个展台,将为产业提供成果展示与交流合作平台。大会旨在助力EDA产业提升影响力,促进EDA工具发展和创新以及促进EDA产业的交流合作。

我要收藏

个赞

评论排行