IIC Shanghai 2024 | Cadence 引领 AI 浪潮,探索芯片设计智能之路

【ZiDongHua 之设计自动化收录关键词:AI 楷登 自动驾驶 电动汽车 机器学习 】

IIC Shanghai 2024 | Cadence 引领 AI 浪潮,探索芯片设计智能之路

3 月 28 日-29 日,2024 国际集成电路展览会暨研讨会(IIC Shanghai)在上海成功举行。此次盛会汇聚了集成电路产业的众多领军人物,共同探寻和把握集成电路产业的发展脉络。

在 29 日举行的 2024 中国 IC 领袖峰会上,Cadence 数字产品资深高级总监刘淼发表了题为《当汽车电子遇见 3D-IC》的精彩演讲;而在同期举行的主题技术论坛上,Cadence 资深技术支持总监王辉、Cadence 资深产品技术销售经理万理也分别发表了题为《Cadence Optimity——利用 AI 应对系统级分析挑战》和《Cadence AI——芯片级到系统级的全栈式智能 EDA 解决方案》的精彩演讲。

刘淼

当汽车电子遇见 3D-IC

2024 中国 IC 领袖峰会

在 2024 中国 IC 领袖峰会上,刘淼阐述了汽车电子与 3D-IC 结合的未来趋势,深入剖析了当前电子世界的主要驱动力,并分享了 Cadence 的创新解决方案。他表示:“创新是我们的基因,我们 30% 的投资用于研发,这也支撑了 Cadence 在过去三年推出了 20 个重量级的新产品。”

刘淼认为,在技术驱动因素对多个行业的影响下,半导体行业正经历前所未有的快速增长。尽管 2023 年全球半导体市场有所下滑,但随后强劲复苏,预计在今年将有超过 10% 的增长率。其中,汽车电子技术的进步将对行业的发展起到重要推动作用。

1

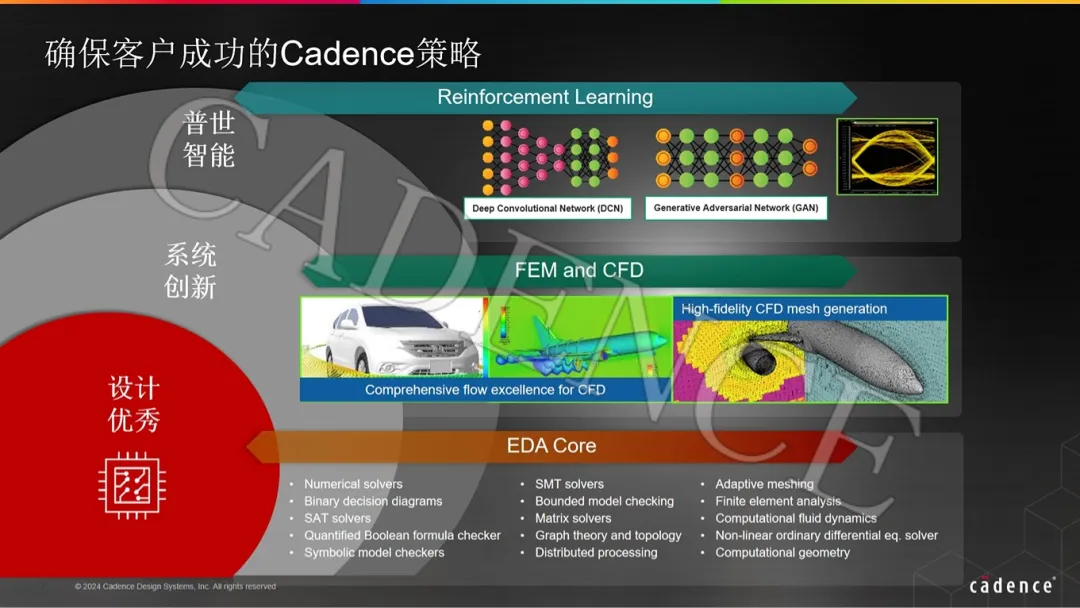

Cadence 的策略是确保客户成功

在介绍 Cadence 策略时,刘淼强调了三个同心圆概念:硅圈、系统圈和数据圈。三个圈相互关联,紧密结合,共同推动芯片、系统和数据的发展。

例如自动驾驶,既依赖导航和场景等海量数据,还需要高效安全的系统,包含硬件、软件和复杂的芯片,而硬件由越来越多、越来越复杂的芯片组成。

35 年来,Cadence 在 EDA 领域的优势主要体现在计算软件——计算机科学加数学,包括实现计算的硬件。无论是硅 EDA 和 IP、大数据系统设计和分析,还是人工智能(AI),Cadence 都展现了强大实力。

他指出,如今人工智能已成为一种新的流行,而作为矩阵乘法的神经网络推理,利用反向传播训练神经网络能实现非线性共轭梯度优化,如 Cadence 的 Innovus。Cadence 的丰富经验不仅可用于硅,还可以用于所有系统和 AI,甚至是将 EDA 计算软件用于生物模拟。

2

汽车电子挑战和 Cadence 设计流程

刘淼表示,电动汽车已经成为中国出口最强劲的引擎,而汽车电子是电动汽车最重要的组成部分之一,为了满足电动汽车越来越高的要求,汽车电子也不得不面对越来越复杂的挑战。这些挑战来源于安全、可靠和质量三个方面的要求,例如,更先进的工艺节点,更多的安全岛机制,更及时的通讯速度,更长的使用寿命,和更大规模的数据计算。

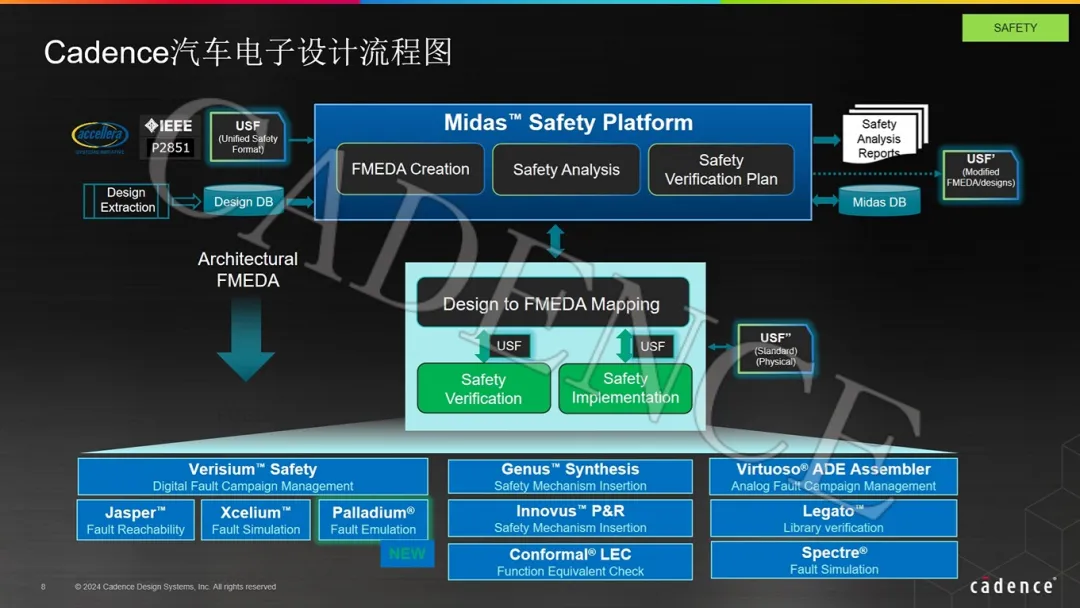

作为汽车电子数字解决方案驱动者,Cadence 与车规芯片厂商、新势力塑造者、创新创业者合作,为他们提供服务、软件、硬件和 IP。

Cadence 的安全意图格式 USF(统一安全格式)是一种与功能安全数据互操作性框架 IEEE P2815 保持一致的格式。USF 贯穿不同设计阶段和产品,确保在整个设计流程中体现安全意图。从预先编写的 USF 文件或 Mida 的 FMEDA 分析开始,能够将 USF 结果交付给相应的验证、实施、混合信号/模拟设计流程,还可以在不同设计团队间轻松交换。

刘淼也做了小小的技术普及,比如数字实现中的安全功能的两个基本应用:TMR 和 DCLS。TMR 通过克隆原始触发器为具有投票逻辑的三元组提供投票机制,以检测和纠正可能的逻辑值错误,增强系统容错能力并提高可靠性。DCLS 则通过双时钟锁定步进方式确保模块级冗余设计,进一步提高系统可靠性。Cadence 完整的 USF 物理实现流程有助于实现车规数字设计。

刘淼还介绍了由中国研发团队实现的任意边界的 DCLS 布局与隔离和检查,这一全新的技术,不光服务了中国的客户,还支撑了 Cadence 在欧洲和北美的车规芯片客户。

Cadnece 在 2023 年推出的最新的带着机器学习加持的 Voltus Insight 电源完整性分析方案。这个全新的分析方案可以和实现工具 Innovus 完美地结合起来,让用户基本无感的,在实现过程中修复绝大部分的压降违例,从而极大提高汽车电子的可靠性,减少 ECO 时间,降低设计成本。

3

后摩尔和超越摩尔时代的 3D-IC

刘淼还从封装级 3D-IC 和晶圆级 3D-IC、同构设计与异构设计、3D-IC 路线图和挑战、键合密度、2.5D 到 3D 等角度强调了后摩尔时代 3D-IC 的重要性。他指出,随着摩尔定律逐渐失效,晶圆级 3D-IC已成为行业的焦点。Cadence既支持封装级、晶圆级 3D-IC,也支持同构和异构设计。从 2.5D 到 3D,其铜-铜键合密度提升了 1000 倍,而传输距离却降低了接近 50 倍,这一先进性,将极大地丰富系统公司从系统方面提升芯片性能的手段。

所以,Cadence 在晶圆级 3D-IC 上取得了长足进展,推出了基于 3D 混合布局的逻辑流内存、适用于同质和非同质芯片组的强大的 3D Mixed Placer。为应对 2.5D 到 3D-IC 的挑战,Cadence 推出了业界首个集成的高容量统一的 Integrity 3D-IC 平台,可在单个统一驾驶舱中进行 3D 设计规划、实施和系统分析。

刘淼最后表示,Cadence 的智能系统设计战略是以计算软件为核心开发的 AI 和算法解决方案,正在扩展到新的系统域。Cadence 还致力于在核心 EDA 和关键 IP 上执行这一战略,并支持云端广泛应用,以实现普适性和可扩展性。

利用 AI 应对系统级分析挑战

Chiplet 与先进封装技术研讨会

在 Chiplet 与先进封装技术研讨会上,Cadence 资深技术支持总监王辉分享了如何利用 AI 技术应对系统级分析挑战,介绍了 Cadence 的 Optimality™ Explorer 智能系统优化助力系统设计突破与创新的能力。

1

应对不断增加的复杂性和规模挑战

王辉指出,随着系统设计复杂性和规模不断增加,传统设计优化方法已难以满足需求,需要用AI技术来应对挑战。Optimality™ Explorer 能加速实现最佳系统级设计性能,为设计师提供强大支持,实现平均 10 倍的设计收敛速度。

他解释道,作为智能系统资源管理器,Optimality™ Explorer 不仅具备快速确定最佳电气性能的能力,还能探索完整设计空间,避免次优局部极小值和极大值,将生产力平均提高 10 倍以上。

Optimality™ Explorer 可扩展解决方案采用AI驱动的多物理优化技术,涵盖模拟、优化和签核等多个方面;突破性算法 Cadence® Cerebrus™ 系统级探索涵盖芯片、封装、板和外壳,能够更全面考虑系统设计的各个方面,实现更优异的性能。

2

AI 新技术为实际设计赋能

谈到 AI 新技术,王辉强调了 Optimality™ Explorer 的强化学习优化能力。与传统设计优化方法相比,它利用强化学习技术预测下一个样本,能更高效地找到最优解。这种“现在到未来”的方案可以使设计师更快获得满意的设计结果。

Optimality™ Explorer 采用突破性的机器学习(ML)算法,以实现最小采样、强化学习技术、全局最优解决方案和首过成功。在提高设计生产力方面,吞吐量提高了 100 倍,实现了大规模并行化和线性可扩展性,且支持云就绪。其应用可扩展到电路图、3D 工作台、3D 布局等多物理场,适用于所有设计阶段。

3

实例展现 Optimality™ Explorer 强大能力

王辉通过实例展示了 Optimality™ Explorer 在实际设计中的应用。从 AI 算法启动设计样本,利用模拟引擎进行分析;由 ML 模型基于初始数据点制定回归模型,优化设计参数并启动新案例。新模拟结果进一步完善了 ML 模型,提高了决策质量,效率提升了 10 倍,接近或优于人类驱动流程。

目前,Optimality™ Explorer 已成功应用于多个系统设计分析与优化实例,如 112Gbps PAM4 通道优化、高维天线优化、三频微带天线参数优化、FPC 差分对参数优化以及 SI/PI 和 RF/天线应用优化,均提升了迭代收敛速度,并显著提高了性能。

王辉表示,多位行业专家已对 Cadence 的 Optimality™ Explorer 赞赏有加,认为 Optimality™ Explorer 和 Clarity™ 3D Solver 等工具帮助他们更快地找到最佳参数配置,加速了产品上市。

他最后表示,通过使用 Optimality™ Explorer 等先进工具,设计师能够更好地应对系统级分析挑战,推动系统设计的不断创新与进步。

万理

芯片级到系统级全栈式智能 EDA 解决方案

EDA 与 IC 设计论坛

在 EDA 与 IC 设计论坛上,万理分享了芯片级到系统级全栈式智能 EDA 解决方案以及如何通过 AI 驱动的优化,实现系统设计的革命性突破。

1

人工智能正在改变设计面貌

万理表示,智能系统时代面临更多挑战,工艺演进使芯片复杂度不断增加,传统设计理念和方法已无法有效应对。利用 AI 驱动的优化能够实现强化学习、卷积神经网络、大型语言模型等;模拟与分析能够涵盖逻辑、电路、SI/PI、CFD、Bio 等多个应用,而计算硬件则适用于 CPU、GPU、FPGA、定制等多种类型设计。

他指出,AI 不仅是人力的补充,从手动电路设计到今天的自动化 RTL 设计重用,每次突破效率都提升了 10 倍;2030 年将再提升 10 倍以上。

他解释说,手动芯片设计优化要从数以百万计的组合中输出,凭借非数值方法和设计师直觉需要 3-6 个月才能达到次优 PPA。AI 可以实现基于现有流程的强化学习,提高电子产品的生产力和质量,并不断改进结果,缩短获得成果的时间。

2

Cadence AI 解决方案为系统设计赋能

Cadence 率先推出了业界首个芯片级到系统级全栈式AI解决方案 Cadence.AI,包括 Cadence® Joint Enterprise Data 和 AI(JedAI)Platform 大数据管理、Cadence Cerebrus™ Intelligent Chip Explorer 数字物理实现、Virtuoso® Studio 模拟开发设计、Verisium AI-Driven Verification Platform 验证、Allegro® X AI Technology 系统设计以及Optimality™ Intelligent System Explorer 系统优化等六大平台。

万理说,Cadence.AI 生成式 AI 技术、JedAI Platform 和一系列 AI 增强工具都在为系统设计提供强大支持,有助于个人和团队实现 IP 和 SoC 创建,满足 AI 驱动的验证、调试、实施和 PPA 优化的生产力需求。

Cadence 的 Joint Enterprise Data 和 AI Platform 可以管理芯片设计数据模型,实现自动选型、智能芯片浏览和芯片设计重构。Cadence 下一代 AI 驱动的验证工作流程 Cadence Verisium™ 可实现失败测试分组等识别错误原因等功能。

Virtuoso Studio 可以进行 AI 驱动的自定义设计,实现电路优化和布局生成。而采用 Allegro X AI 的 AI 驱动的 PCB 设计可将数天的手动流程转缩短到数小时,效率提高 10 倍以上。

Optimity™AI 驱动的系统分析平台可将汽车 PCB 验证效率提高 30 倍,改善 DDR4 BGA 封装插入损耗多达 134%,112G PAM4 SerDes 隔离性能提高 1260%;而 AI 驱动的 3D-IC 可优化 Chiplet 和封装设计。

万理最后总结道,Cadence.AI 以前所未有的方式定义了 EDA 2.0,引领半导体设计的未来,让工程师专注于更具创新性的工作,极大地提升工程团队的生产效率,让系统设计更加高效、智能和可持续。

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。

© 2024 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

我要收藏

个赞

评论排行