ISEDA 2024圆满落幕,带您解锁合见工软精彩亮点

【ZiDongHua 之设计自动化收录关键词: EDA 人工智能 汽车电子】

硬核回顾 | ISEDA 2024圆满落幕,带您解锁合见工软精彩亮点

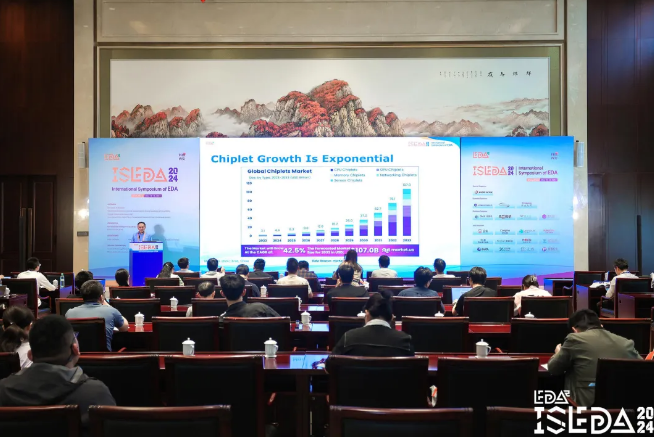

2024年5月10日-5月13日,年度国际学术大会2024 International Symposium of EDA(ISEDA 2024)在西安陕西宾馆成功召开。

合见工软受邀参与,携数字芯片全流程EDA产品、系统级产品设计全流程解决方案、全国产IP解决方案亮相ISEDA 2024。合见工软首席技术官贺培鑫博士受邀出席本次会议并发表重磅演讲——《如何提高通过大语言模型生成Verilog RTL代码的准确性》、《芯粒探索器:通过自动化的解决方案空间探索,优化多芯粒集成芯片》,分享交流了EDA领域的前沿技术和合见工软的最新研发成果。

生成式AI:

数字芯片验证的未来突破

在当今的生成式AI时代,大语言模型(LLM)也为EDA技术带来了巨大机遇, 体现在芯片设计和验证过程中,通过AI技术加持,未来有望实现用更少的时间完成芯片设计和验证工作,从而大幅缩短芯片设计周期,加速产品上市。

近期,OpenAI的ChatGPT、谷歌的Gemini和GitHub的Copilot,已经展示了从自然语言描述或代码框架中生成代码的能力,这跨越了多种软件编程语言,包括Python、JavaScript和C++。然而,在为IC设计生成Verilog RTL代码时,这些大语言模型在语法和语义方面都面临着高准确性的挑战。

在5月11日的专题研讨会《智能电路:利用人工智能实现高效的逻辑设计和验证》中,贺培鑫博士发表了演讲《如何提高通过大语言模型生成Verilog RTL代码的准确性》。作为第一位演讲嘉宾,贺培鑫提出通过LLM生成Verilog RTL代码具有广阔的发展前景,但面临着诸多挑战:开源Verilog代码的数量较少,如何更有效地训练EDA LLM?芯片成本很高,如何生成更准确的RTL代码、减少bug?EDA LLM如何应对结果质量QoR (Quality of Result) 评估的挑战?IC设计基本都是大项目,因此Verilog RTL的小模块非常多,如何处理这么多模块?硬件工程师数量少于软件工程师,EDA LLM工具的商业模式如何做?

贺培鑫介绍了一种改进的LLM模型,能够显著提高生成Verilog RTL代码的准确性。该模型还能够与软件仿真器、调试器等工具集成,更好地帮助IC设计师调试软件仿真结果,比如AI可以生成简单的或者通用的测试向量,用户为了更好地验证功能可以对生成的测试向量进行改进,随后AI会在对应的阶段自动调用软件仿真器、调试器。该模型也能够与逻辑综合工具集成,预测面积、时序等,比如AI可以建议为某个时钟加上时钟门控 (clock gating) 来降低功耗。该模型通过500多个Verilog RTL代码生成和补全的测试用例进行了准确性的实验验证。

合见工软正在积极布局AI驱动EDA工具的进程中,该LLM引擎将与合见工软的多款产品进行结合,促进下一代全新的EDA工具技术演进。贺培鑫表示,对于EDA公司来说,相信AI能够大幅提升工作效率,但我们不应该担心被AI取代,而应该担心被会使用AI的人取代;对于芯片公司,也就是我们的客户来说,敏捷高效的公司应该要充分利用AI。

在专家研讨环节,针对“大模型时代,数字电路设计与验证的挑战与机遇”,贺培鑫表示在HPC、GPU、AUTO等应用领域,都需要用到大算力芯片,而芯片验证是芯片设计过程中的关键环节,尤其在硬件仿真、原型验证阶段,如何为大芯片做设计分割、加快验证时间等问题越来越复杂,相信随着AI在EDA领域的不断发展,未来AI能够协助IC设计工程师更高效地完成验证工作。当然,目前的LLM还做不到直接设计一块芯片,但我们可以把设计流程拆分成若干阶段,尝试将任务分解给AI来做。

合见工软在芯片级EDA领域已率先推出针对数字芯片验证的EDA全流程平台工具,包括商用级、高性能的数字仿真器UniVista Simulator (UVS),全场景验证硬件系统UniVista Unified Verification Hardware System (UVHS)等核心产品 。合见工软也正在自研大数字芯片的核心IP,已实现Memory Interface、PCIe Gen5 和 RDMA/Ethernet等完整解决方案的全国产化。以上产品均涉及RTL代码的编写,给LLM带来发挥空间。可以预见,为IC设计定制化的大语言模型将成为EDA工具发展的趋势。合见工软将坚持自主研发、开拓创新,致力于提供世界一流水平的EDA产品。

Chiplet异构集成:

催生Chiplet EDA设计平台

近年来,摩尔定律因为成本问题正在放缓,但高性能计算HPC的性能依然能够做到指数级增长,这重点归功于Chiplet技术的快速发展。根据market.us的数据分析,未来十年全球Chiplet市场的年复合增长率将达到42.5%,预计2033年市场规模将达到1070亿美金。当前全球最先进的芯片都在使用Chiplet异构集成技术,如AMD MI300芯片使用了13个Chiplet,包括GPU、CPU、HBM3等。

在5月12日的Technical Session 15《Chiplet and 3DlC Revolution & High-Level Synthesis Frontier》中,贺培鑫博士发表了演讲《芯粒探索器:通过自动化的解决方案空间探索,优化多芯粒集成芯片》,提出Chiplet异构集成技术的发展在系统层面,对延续摩尔定律至关重要。然而,Chiplet也面临着如性能优化、能效、信号和电源完整性、热管理、可测性设计(DFT)等方面的挑战,这些也是Chiplet EDA设计工具需要做到的功能。

贺培鑫认为,设计Chiplet异构集成方案时,需要考虑四个关键维度。首先,该芯片需要用到多少个Chiplet?每个Chiplet中使用哪些逻辑功能模块?完成功能定义后,要考虑每个Chiplet用什么工艺,成熟工艺还是先进工艺?确认工艺后,Chiplet之间用什么互连技术,如2D、2.5D、3D?用什么互连协议IP,如UCIe、HBM3?最后,如何在基板上布局Chiplet?

贺培鑫介绍了一种Chiplet设计自动化的创新方法,利用EDA工具和IP,帮助设计工程师在使用多个Chiplet异构集成芯片时,自动化生成Chiplet设计方案,更好地权衡PPA、制造工艺、成本等因素,从而发现利用多样化Chiplet的更优解决方案。该方法主要包括如下步骤:第一步,基于Chiplet参数、集成技术、IC的布局规划、I/O布局、工艺设计套件PDK (Process Design Kit) 进行布局,这是自动化的IC级线长和密度驱动的布局。第二步,用户选择需要构成Chiplet的模块,以及相应的PDK、集成方法。第三步,根据用户的输入,自动计算Chiplet的尺寸和位置,插入互连IP,通过物理实现工具估测面积、拥塞、时序和功耗,根据仿真结果判断是否返回第二步。第四步,进行板级的布线、SI/PI仿真、热仿真,根据仿真结果判断是否返回第二步。

合见工软正在基于此方法研发Chiplet EDA设计平台,全面布局Chiplet IP、芯片级设计、系统级封装等工具,目前已实现全国产 Chiplet接口 和 IO Die 完整解决方案,已发布面向Chiplet的先进封装协同设计Sign-Off检查和优化工具UniVista Integrator (UVI)。

EDA多维演进:

共建AI+Chiplet新生态

活动期间,合见工软展台也全程陪伴,展示了合见工软的EDA多维演进战略、全场景验证硬件布局,驾驭“AI+Chiplet”对EDA的新挑战,吸引众多观众,引发热烈的学术探讨与产业交流。

◀左右滑动查看更多 ▶

合见工软现已推出多款自主自研的EDA与IP产品,产品覆盖全场景数字验证硬件、虚拟原型验证平台、功能仿真、验证管理及系统级原型验证、IP验证,及可测性设计DFT、电子系统板级和先进封装设计研发管理,高速接口IP等。多产品线并行研发,构筑了“芯片-软件-系统-应用”的芯片与整机系统联动设计与产业生态,有力支撑中国芯片行业发展。产品面世以来,已经在高性能计算、5G通信、GPU、人工智能、汽车电子等国内头部企业中成功部署应用,全面展示了合见工软公司产品强大的技术实力与研发能力。

合见工软的EDA与IP工具平台包括:

▶商用级、高性能、全场景验证硬件系统UniVista Unified Verification Hardware System(简称“UVHS”)

▶商用级虚拟原型设计与仿真工具套件UniVista V-Builder/vSpace

▶商用级、高效测试向量自动生成工具UniVista Tespert ATPG

▶全新一代UniVista EDMPro电子系统研发管理平台

▶首款自主知识产权的全国产PCIe Gen5完整解决方案UniVista PCIe Gen5 IP

▶数字仿真器/调试器UniVista Simulator/UniVista Debugger

▶原型验证系统UniVista Advanced Prototyping System

▶先进封装互连检查工具UniVista Integrator

▶原理图设计环境 UniVista Archer Schematic和PCB设计环境 UniVista Archer PCB

ISEDA 2024圆满落幕,

合见工软期待与您来年再会

我要收藏

点个赞吧

平台转发数:1次

评论排行