MLSynthesis v1.0 版本发布:重大特性升级!

【ZiDongHua 之设计自动化收录关键词:生成器 函数开关 电子设计自动化 】

MLSynthesis v1.0 版本发布:重大特性升级!

高层次综合(HLS):现代设计的新方向

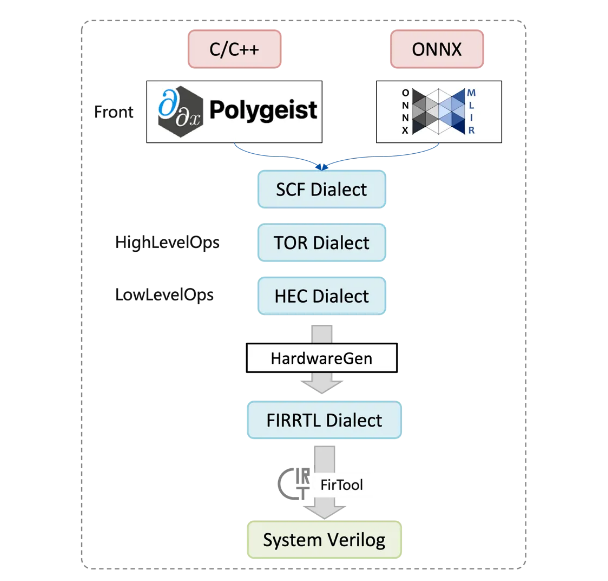

高层次综合(HLS)技术正在改变设计方式。它能够将高层次语言(如C、C++、SystemC)描述的逻辑结构,转化为低抽象级语言(如Verilog、VHDL、SystemVerilog)描述的电路模型。高层次语言让设计者无需关注繁琐的时钟和时序细节,而低层次语言则精确描述了时钟周期的寄存器传输级电路模型,在当前的FPGA敏捷开发设计中被广泛使用。

MLSynthesis v1.0 版本发布:

重大特性升级

我们很高兴地宣布,MLSynthesis v1.0版本已完成,带来了诸多重要特性升级:

01

升级LLVM到llvm18版本

新版本包括更多编译器优化,同时升级了对应的MLIR版本,提升了整体性能和编译效率。

02

硬件生成器后端

升级为FIRRTL

原有基于Chisel生成Verilog的流程较为复杂,需要依赖mill和sbt等工具,且Chisel转Verilog过程中存在不确定性。在状态机规模较大(STATE>200)时,可能会出现Java内存溢出问题,限制了大规模应用。此外,由于Chisel本身缺乏testbench,验证工作需要额外的后端支持,增加了用户测试的难度。

CIRCT项目(Circuit IR Compiler and Tools)是基于电路中间表示(IR)的编译器和设计工具。MLSynthesis v1.0 引入了firtool工具,能够将FIRRTL Dialect转换为SystemVerilog,并自动生成对应的testbench测试工具,用户只需提供相应的测试文件即可完成端到端测试。

03

增加对Vivado IP的支持,

并实现端到端运行

以Xilinx的IP为例,MLSynthesis v1.0 将Xilinx的三十多种IP集成到软件中,支持四五十种不同的运算。同时,软件生成对应的TCL脚本,实现FPGA仿真验证。

04

增加struct支持

提供对C语言struct的全面支持,提升了代码的组织和管理能力。

05

增加inline pragma

内联函数开关

函数内联能够消除函数调用的开销,并共享和优化函数内部的运算。MLSynthesis v1.0默认对除递归函数外的所有函数自动进行内联。若需关闭内联,可在被调用函数内使用#pragma HLS inline off,函数将不会被内联。

06

修复诸多bug

新版本中,我们还修复了许多已知问题,进一步提升了系统的稳定性和可靠性。

希望这个版本的MLSynthesis v1.0能为您的开发工作带来更多便利与效率。感谢您对我们的支持!

我要收藏

点个赞吧

平台转发数:1次

评论排行